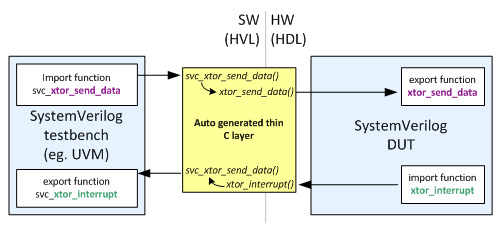

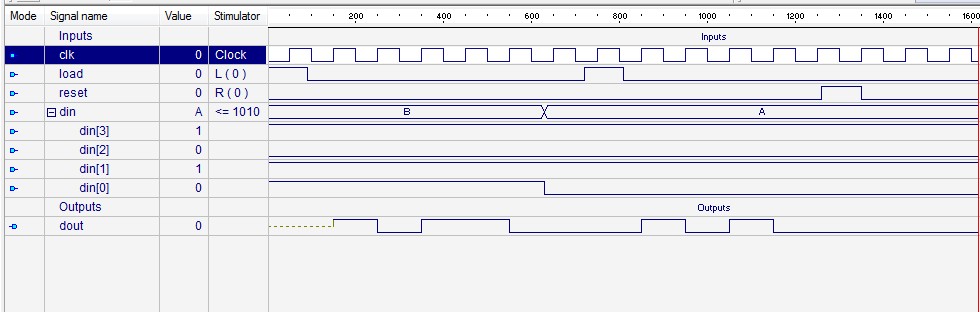

A test bench was developed to verify the SPI master core. The focus is to understand how OOT and SystemVerilog improve productivity and functional coverage in a verification environment by the use of different constructs, constrained-random techniques, coverage, and assertions. This paper provides an understanding of the verification, layered test benches, Object-Oriented Technology (OOT), SystemVerilog, SPI features, SPI advantages, disadvantages, and applications, SPI data transmission and transfer formats, SPI registers, SPI sub-system and Wishbone-SPI architecture, and the test bench development methodology. An existing design from Open Cores is re-used, described as per latest specifications in Verilog at the Register Transfer Level (RTL) and is in conformity with the design-reuse methodology. This research presents a verification environment using SystemVerilog for the SPI Master device.

Both the hardware buses employ a master-slave configuration which makes the bus-interfacing easier. An open source hardware computer bus Wishbone is selected as the host controller enabling parallel data exchange for faster communication. SPI is the core controller of the design. SPI is widely used and advantageous over other serial interfaces due to its features of simplicity, low cost, clock synchronous, and non-interrupting high-speed data transfer rate. The common serial interfaces include Serial Peripheral Interface (SPI), Inter-Integrated Circuit (I2C), Universal Asynchronous Receiver Transmitter (UART), and Universal Serial Bus (USB).

A number of Integrated Circuit (IC) manufacturers develop and produce components that are compatible with serial interfaces. Synchronous serial interfaces provide economical on-board communication between the processor, digital to analog and analog to digital converters, memory, and other building blocks on the chip.

0 kommentar(er)

0 kommentar(er)